很多程序员每天写着 Java、Go、Python,却很少思考一个问题:

代码最终是如何在物理世界里运行的?

从一堆沙子到CPU,从缓存一致性协议到JVM优化,这条链路决定了软件系统的性能上限。

这篇文章试图带你从物理层一路走到软件层,理解计算机体系的核心逻辑。

一、核心问题:数字如何在物理世界表示?

计算机本质上解决的是一个问题:

如何用物理现象表示数字?

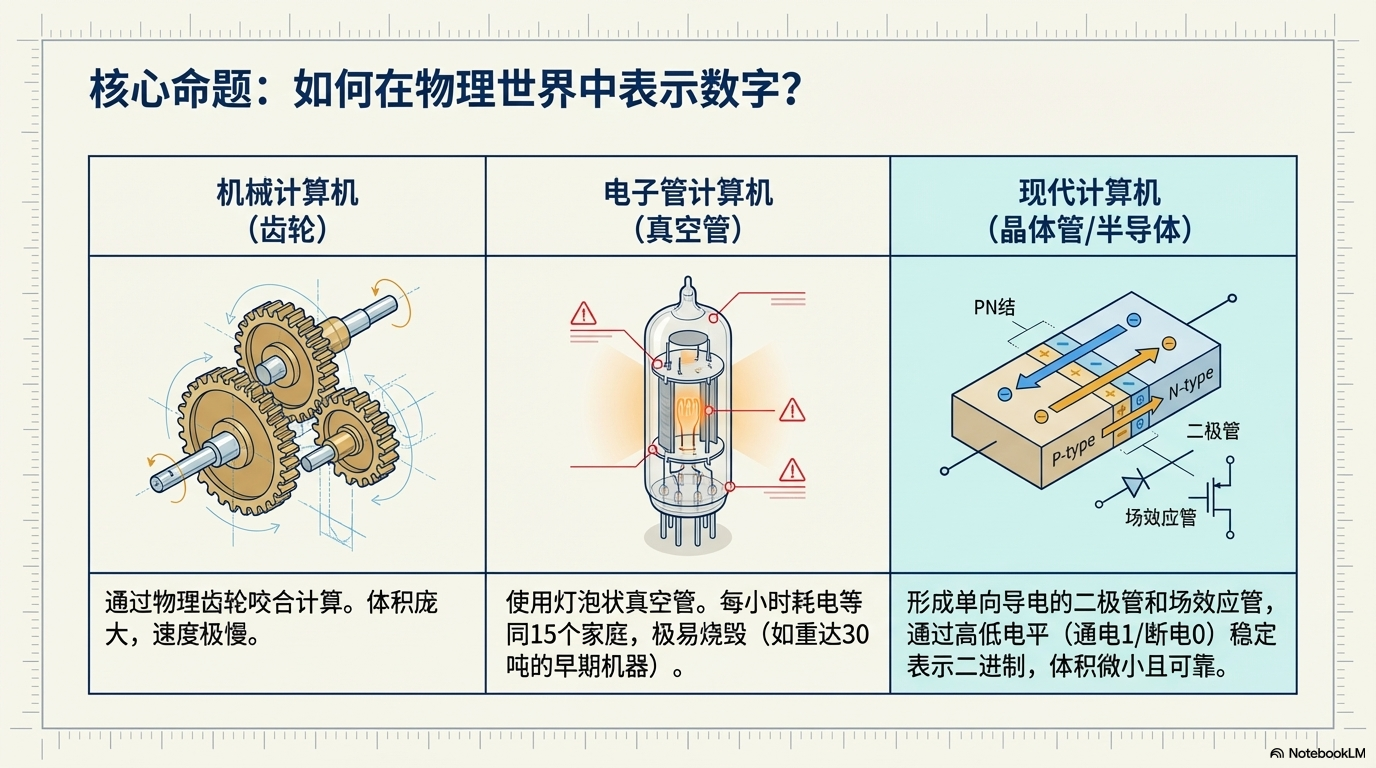

计算机的发展经历了三次重大形态:

1 机械计算机(齿轮)

最早的计算机依靠机械结构进行计算。

典型代表:巴贝奇分析机。

特点:

- 通过齿轮啮合表示数字

- 体积巨大

- 运算速度极慢

本质是:

物理位置 = 数字

但机械系统的速度和可靠性都无法满足需求。

2 电子管计算机

第二阶段是电子管计算机。

特点:

- 使用真空管控制电流

- 体积巨大

- 功耗极高

- 极易损坏

例如早期计算机:

- 每小时耗电量相当于 15个家庭

- 机器经常烧管

但它带来了一个关键思想:

电信号 = 数字

3 半导体计算机

现代计算机使用的是:

晶体管

核心原理:

通过 PN 结控制电流。

状态表示:

导通 = 1

断开 = 0

于是:

电信号 → 二进制 → 计算

这就是现代计算机的基础。

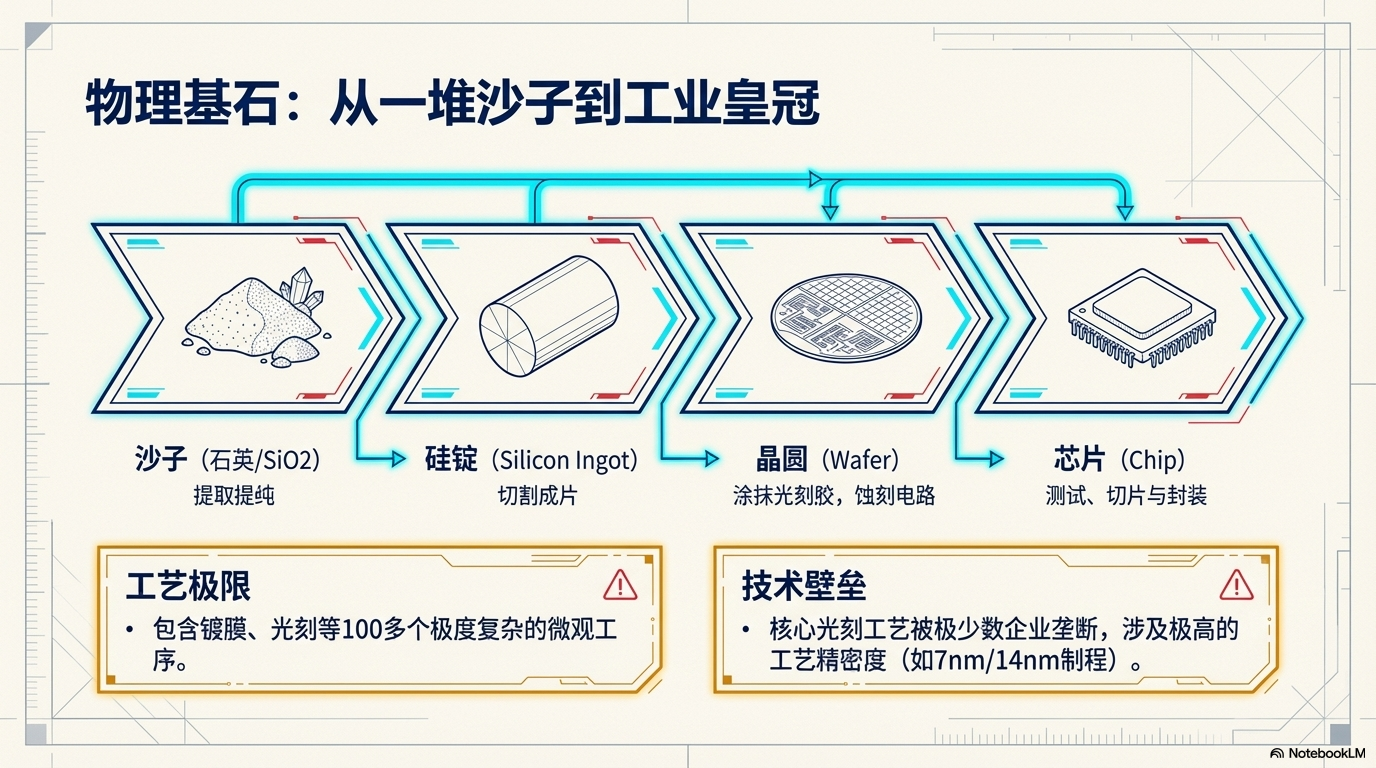

二、从沙子到芯片:计算机的物理基石

很多人不知道:

CPU 的原料其实是 沙子

具体流程如下:

第一步:提纯石英

原料:

SiO2(石英)

提纯得到:

高纯硅

第二步:制作硅锭

将硅熔化后拉成:

硅锭(Silicon Ingot)

第三步:切割晶圆

把硅锭切成薄片:

Wafer(晶圆)

第四步:光刻

通过光刻技术刻蚀电路。

工艺包含:

- 光刻

- 沉积

- 刻蚀

- 掺杂

整个芯片制造包含:

100+道复杂工序

第五步:封装成芯片

最后得到:

CPU Chip

这就是从一堆沙子到芯片的全过程。

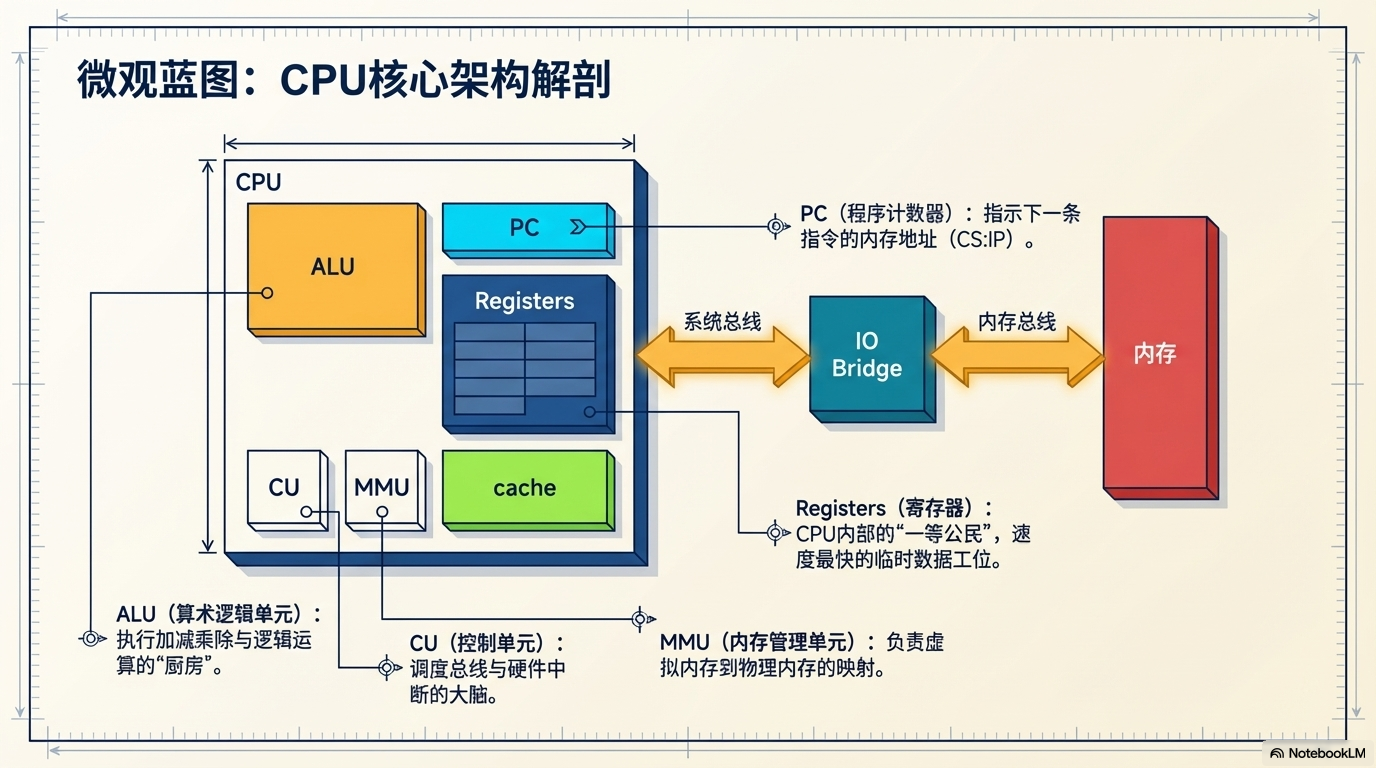

三、CPU内部结构:微观蓝图

CPU内部主要组件:

CPU

├── ALU(算术逻辑单元)

├── Registers(寄存器)

├── PC(程序计数器)

├── CU(控制单元)

├── Cache(高速缓存)

└── MMU(内存管理单元)

核心角色:

1 ALU

负责计算:

- 加

- 减

- 乘

- 除

- 逻辑运算

2 Registers

寄存器是:

CPU内部最快的存储

访问时间:

< 1ns

3 PC(Program Counter)

程序计数器负责:

指向下一条指令地址

4 Cache

CPU 与内存之间的速度缓冲层。

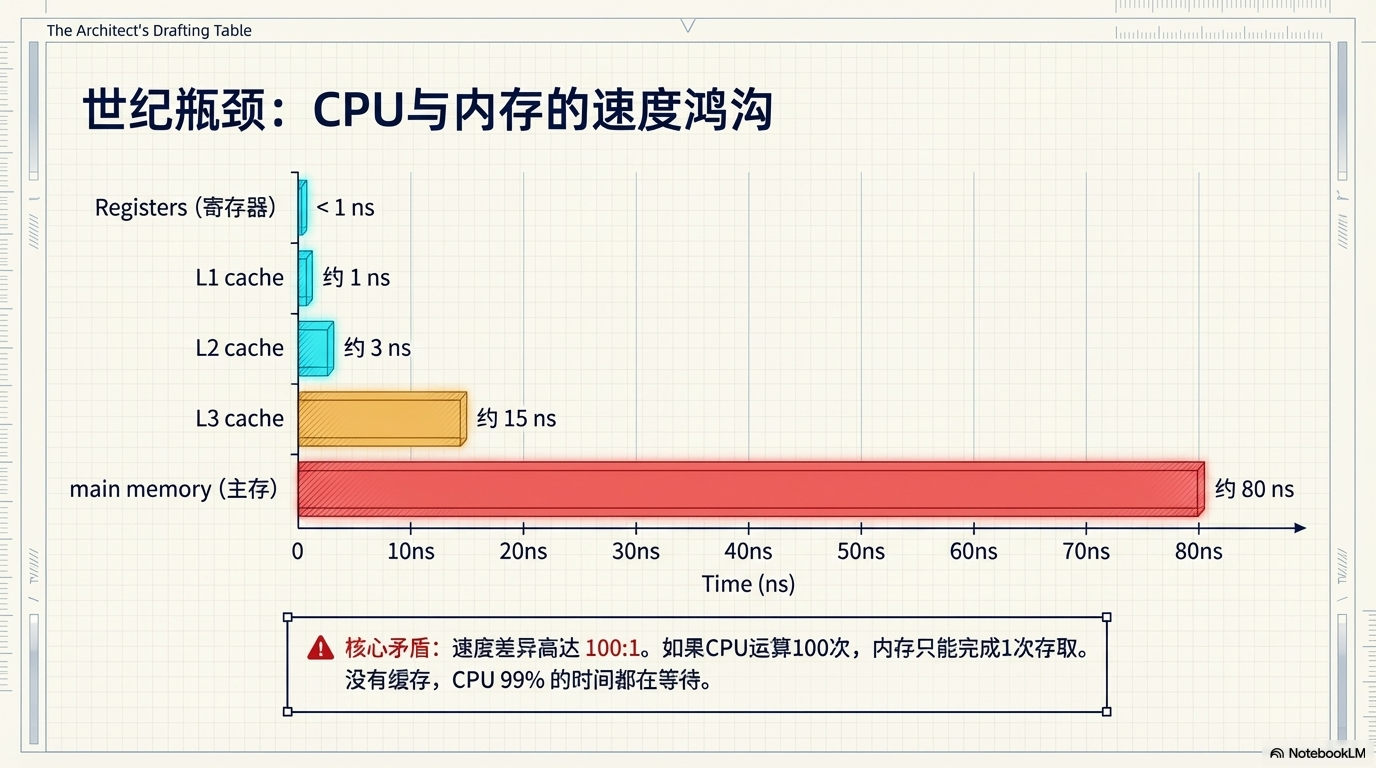

四、世纪瓶颈:CPU 与内存速度鸿沟

CPU 和内存速度差距非常大。

大致延迟:

| 组件 | 延迟 |

|---|---|

| 寄存器 | <1ns |

| L1 Cache | ~1ns |

| L2 Cache | ~3ns |

| L3 Cache | ~15ns |

| 主内存 | ~80ns |

差距:

CPU : Memory ≈ 100 : 1

如果没有缓存:

CPU 99% 时间都在等待内存。

于是产生了:

存储层次结构

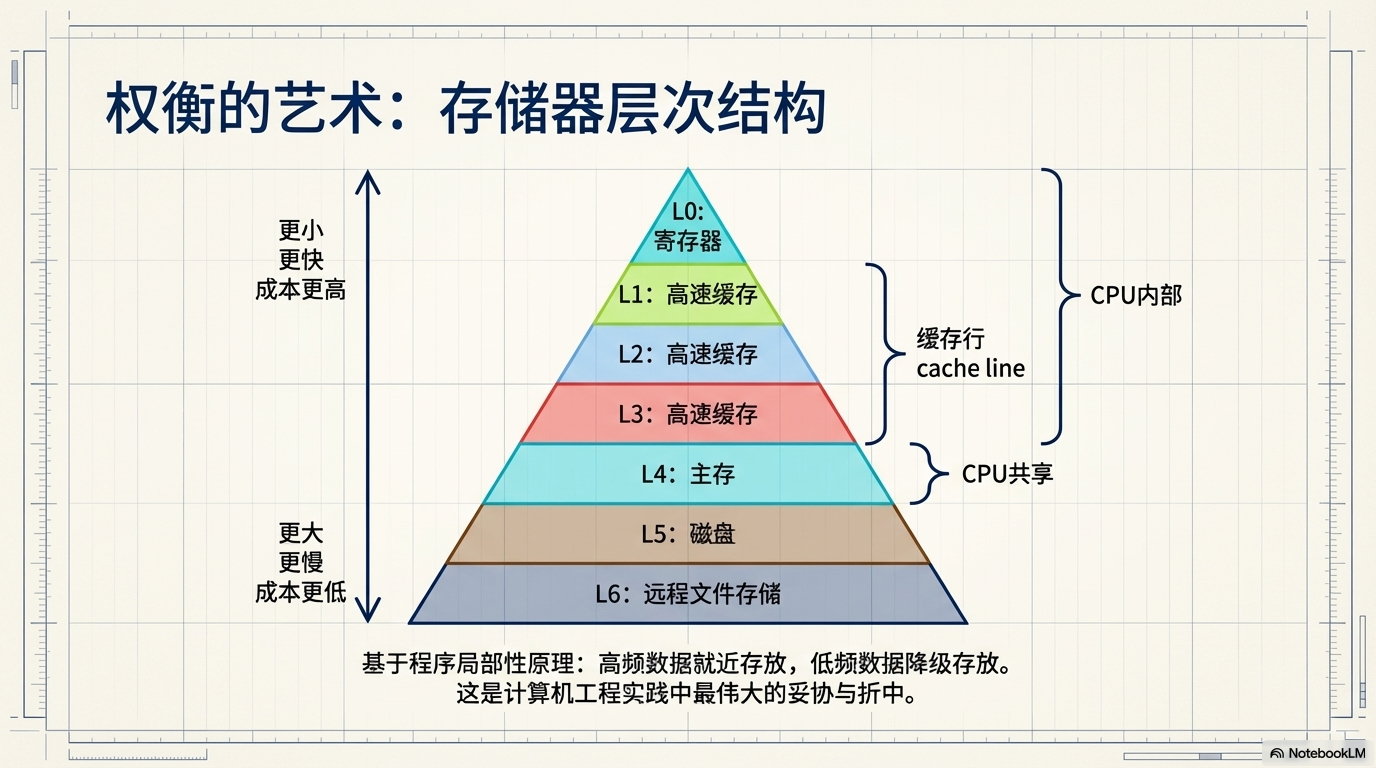

五、存储层次结构

现代计算机的存储结构是一个金字塔:

L0 Registers

L1 Cache

L2 Cache

L3 Cache

L4 Main Memory

L5 Disk

L6 Remote Storage

特点:

| 越往上 | 越往下 |

|---|---|

| 更快 | 更慢 |

| 更小 | 更大 |

| 更贵 | 更便宜 |

设计原则:

局部性原理

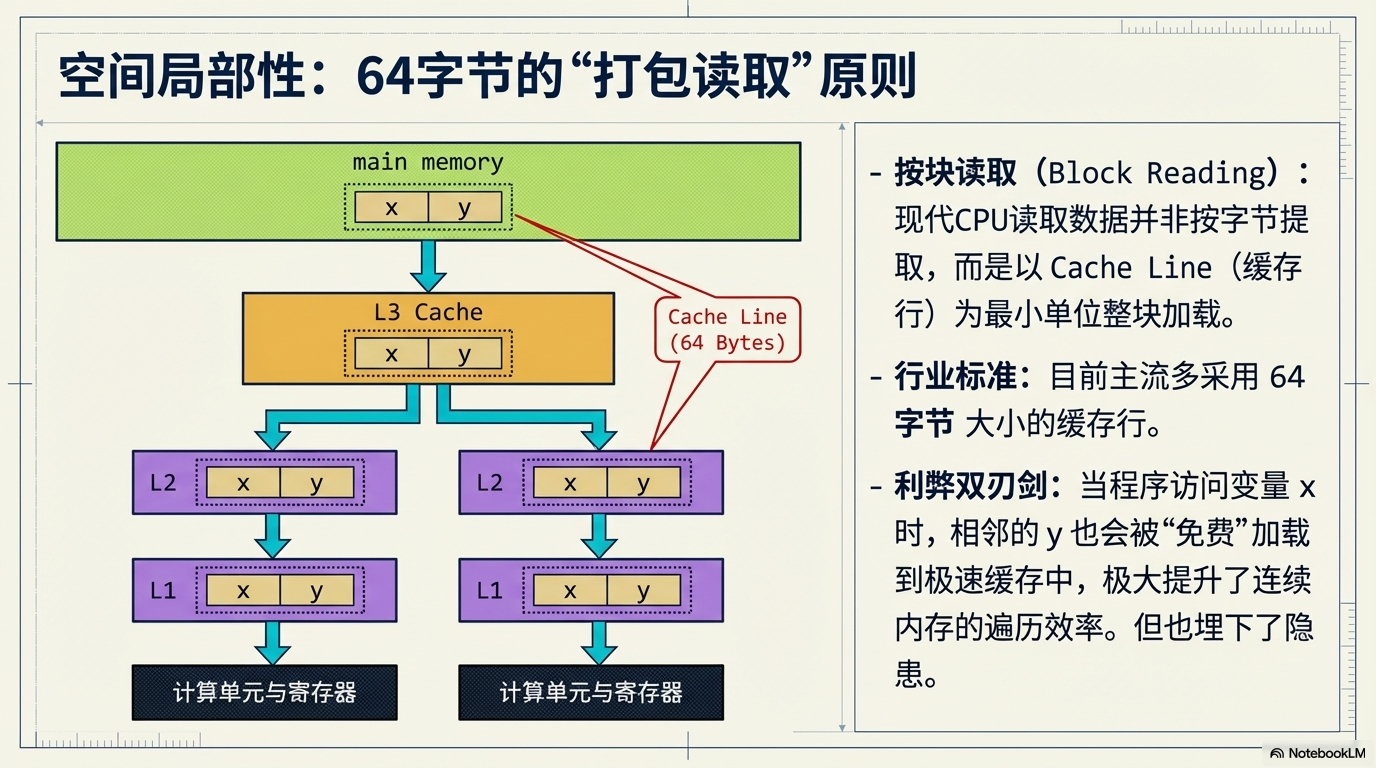

六、空间局部性:64字节缓存行

CPU读取数据并不是按字节。

而是按:

Cache Line

读取。

典型大小:

64 Bytes

例如:

int x

int y

如果访问 x:

CPU会把 x 和 y 一起加载到 cache。

好处:

连续访问速度极快

但也埋下一个隐患。

七、多核问题:缓存一致性

多核CPU会出现问题:

多个核心各自有缓存。

如果:

CPU A 修改变量

CPU B 也有缓存

怎么办?

解决方案:

MESI协议

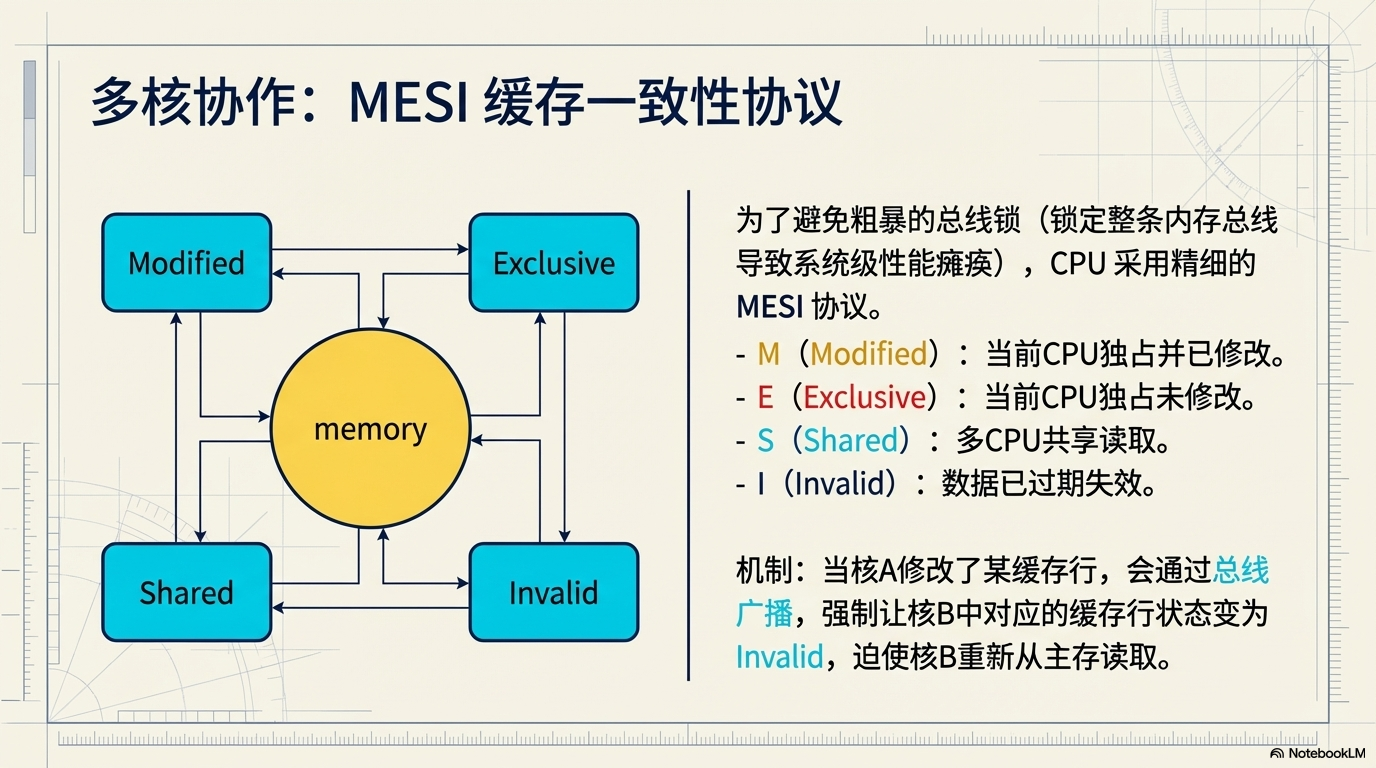

八、MESI 缓存一致性协议

MESI 包含四种状态:

| 状态 | 含义 |

|---|---|

| M | Modified |

| E | Exclusive |

| S | Shared |

| I | Invalid |

流程:

当一个 CPU 修改数据:

广播消息

其他 CPU:

缓存失效(Invalid)

然后重新从内存读取。

这种机制保证:

缓存一致性

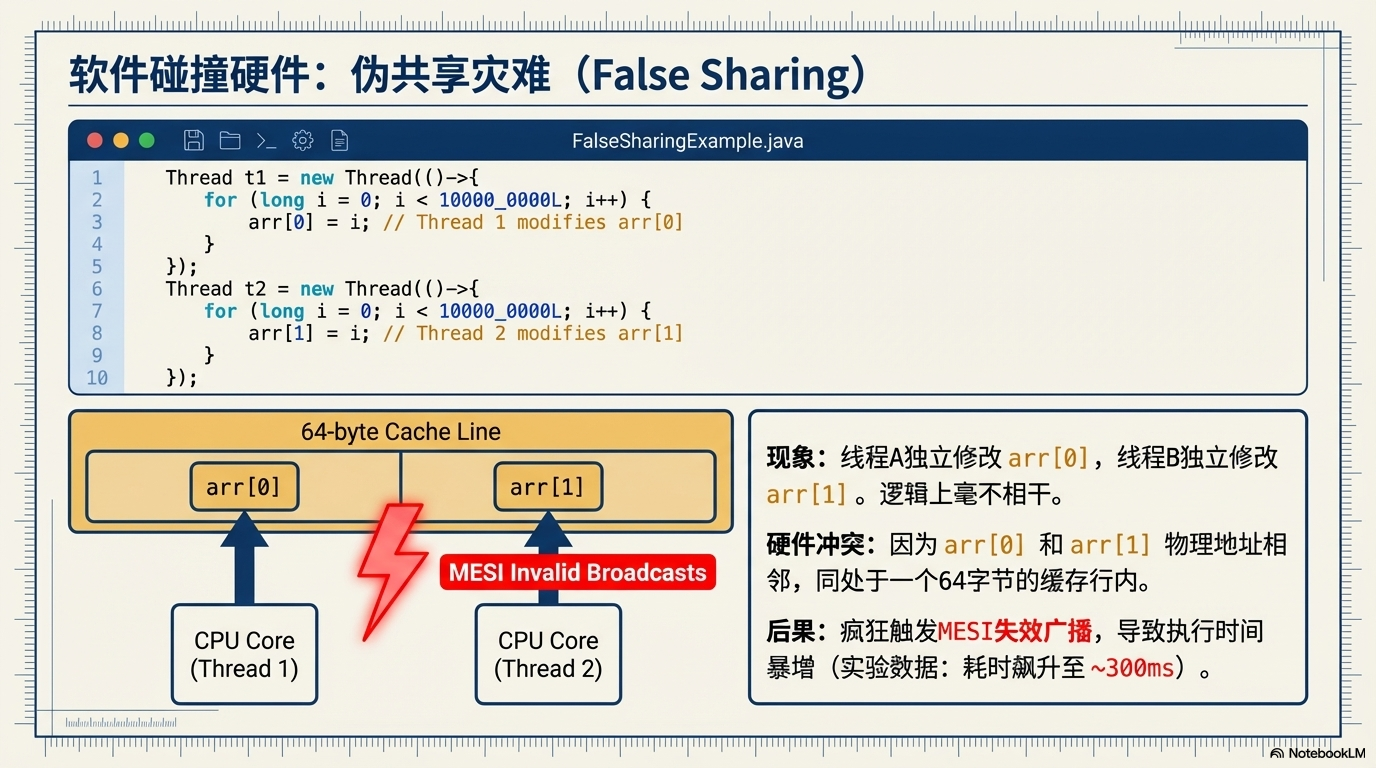

九、软件撞上硬件:伪共享

多线程程序经常出现一个问题:

False Sharing(伪共享)

示例:

arr[0]

arr[1]

线程 A 修改:

arr[0]

线程 B 修改:

arr[1]

逻辑上互不影响。

但如果:

arr[0] 和 arr[1]

在同一个 cache line

就会导致:

MESI疯狂失效

最终性能暴跌。

例如:

执行时间:300ms

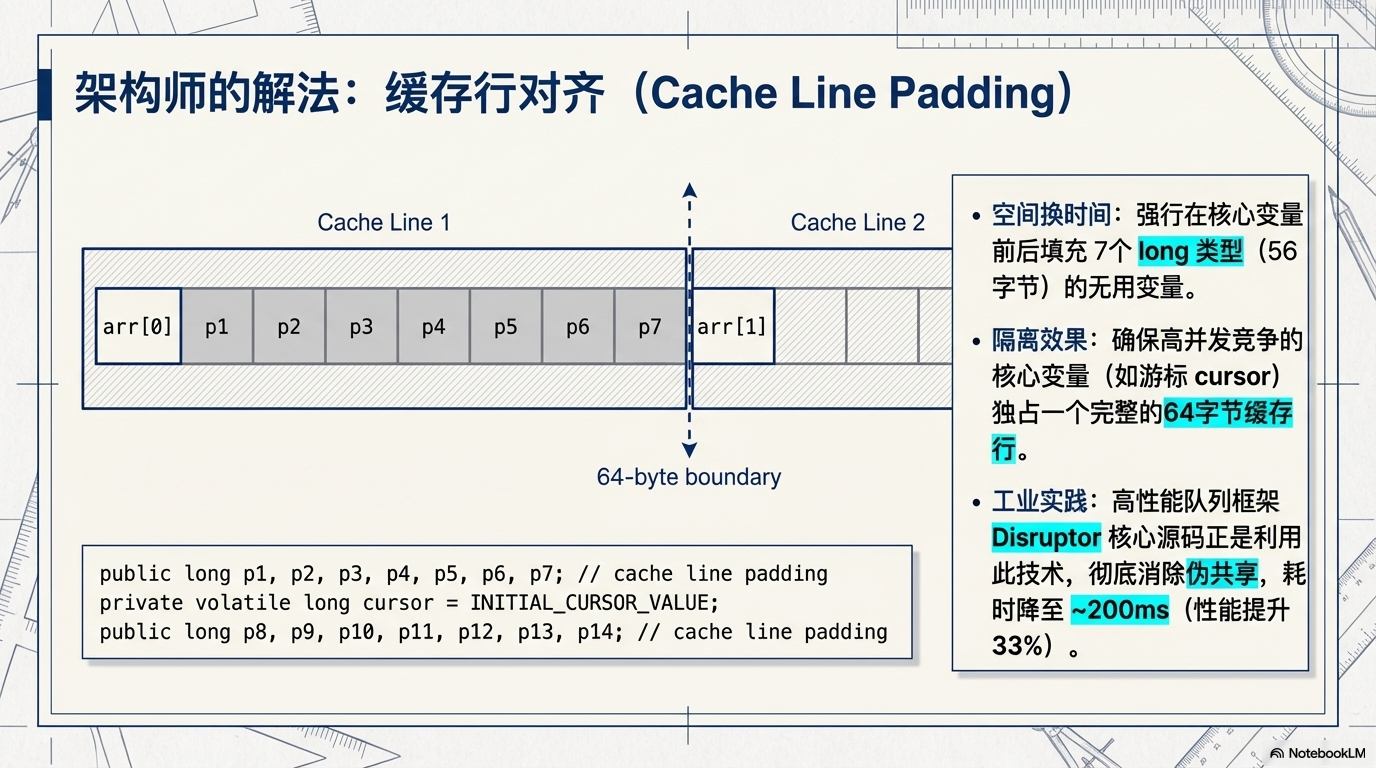

十、解决方案:缓存行填充

架构师常用技巧:

Cache Line Padding

方法:

让关键变量独占一条缓存行。

例如:

long p1,p2,p3,p4,p5,p6,p7;

volatile long cursor;

long p8,p9,p10,p11,p12,p13,p14;

填充:

7个 long = 56 Bytes

加上变量:

≈ 64 Bytes

这样:

cursor 独占一条缓存行

效果:

避免伪共享。

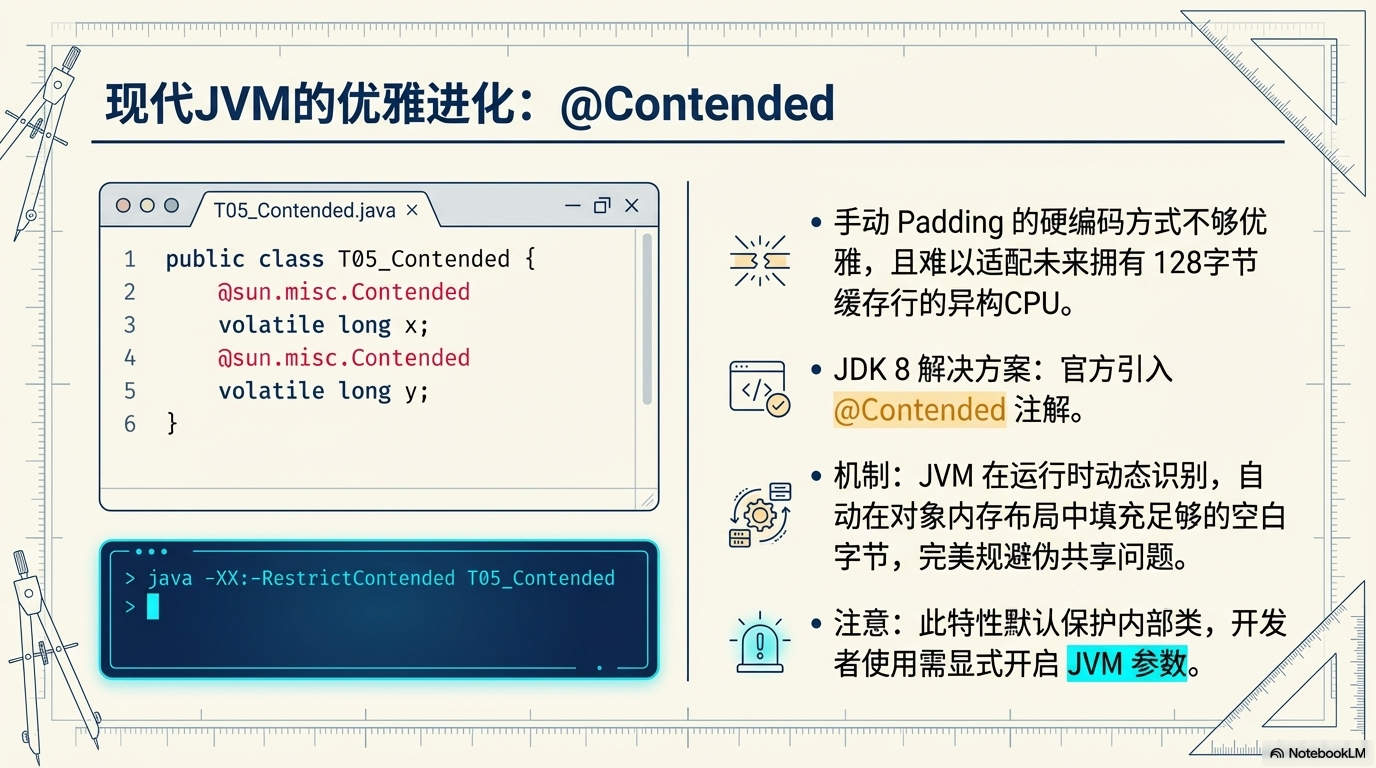

十一、JVM 的优雅方案:@Contended

手动 padding 有问题:

- 不优雅

- 不可维护

- 不适配未来 CPU

因此 JDK8 提供:

@Contended

示例:

public class T05_Contended {

@sun.misc.Contended

volatile long x;

@sun.misc.Contended

volatile long y;

}

JVM会自动:

填充缓存行

避免伪共享。

使用时需要开启参数:

-XX:-RestrictContended

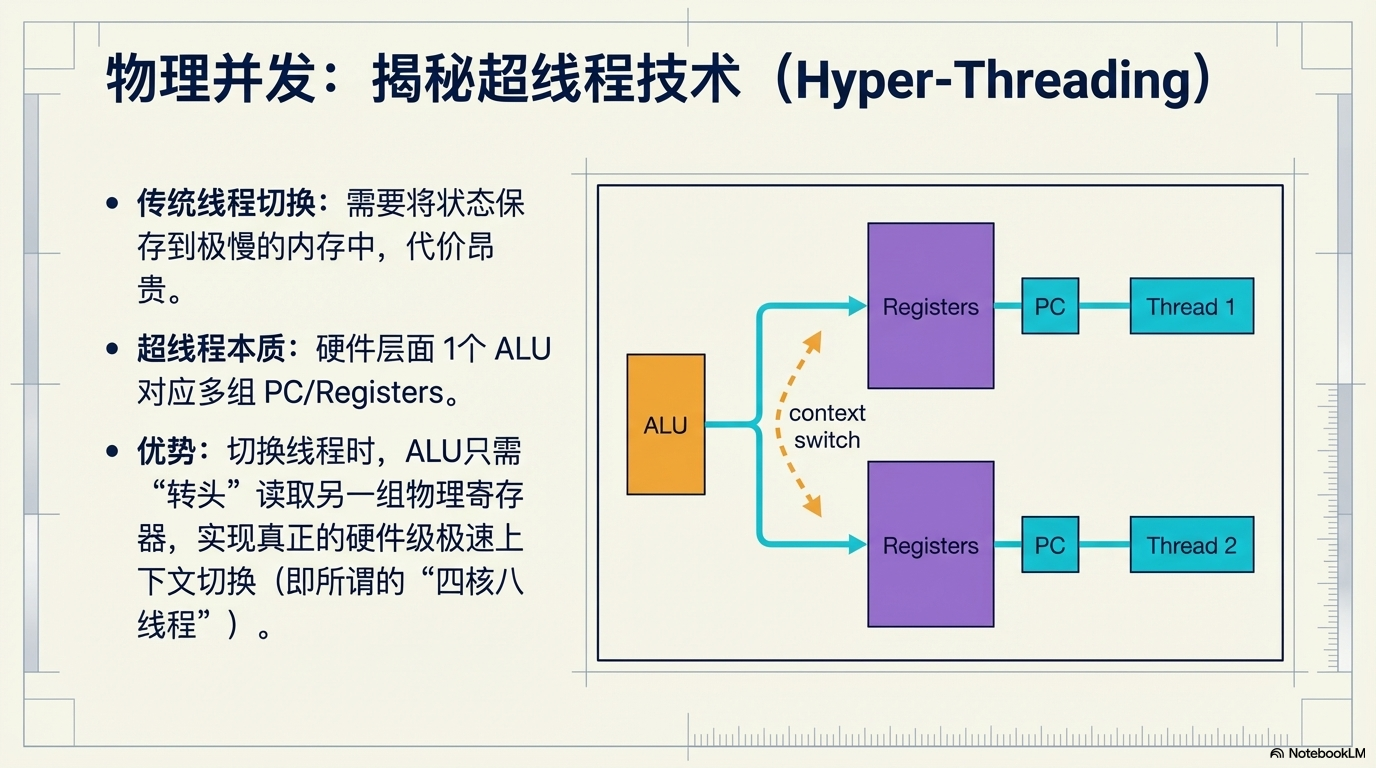

十二、物理并发:超线程技术

传统线程切换:

保存上下文 → 写入内存 → 恢复

成本很高。

超线程技术的核心思想:

一个 ALU

多组寄存器

这样 CPU 可以:

快速切换线程

不需要写回内存。

例如:

4核 CPU

→ 8线程

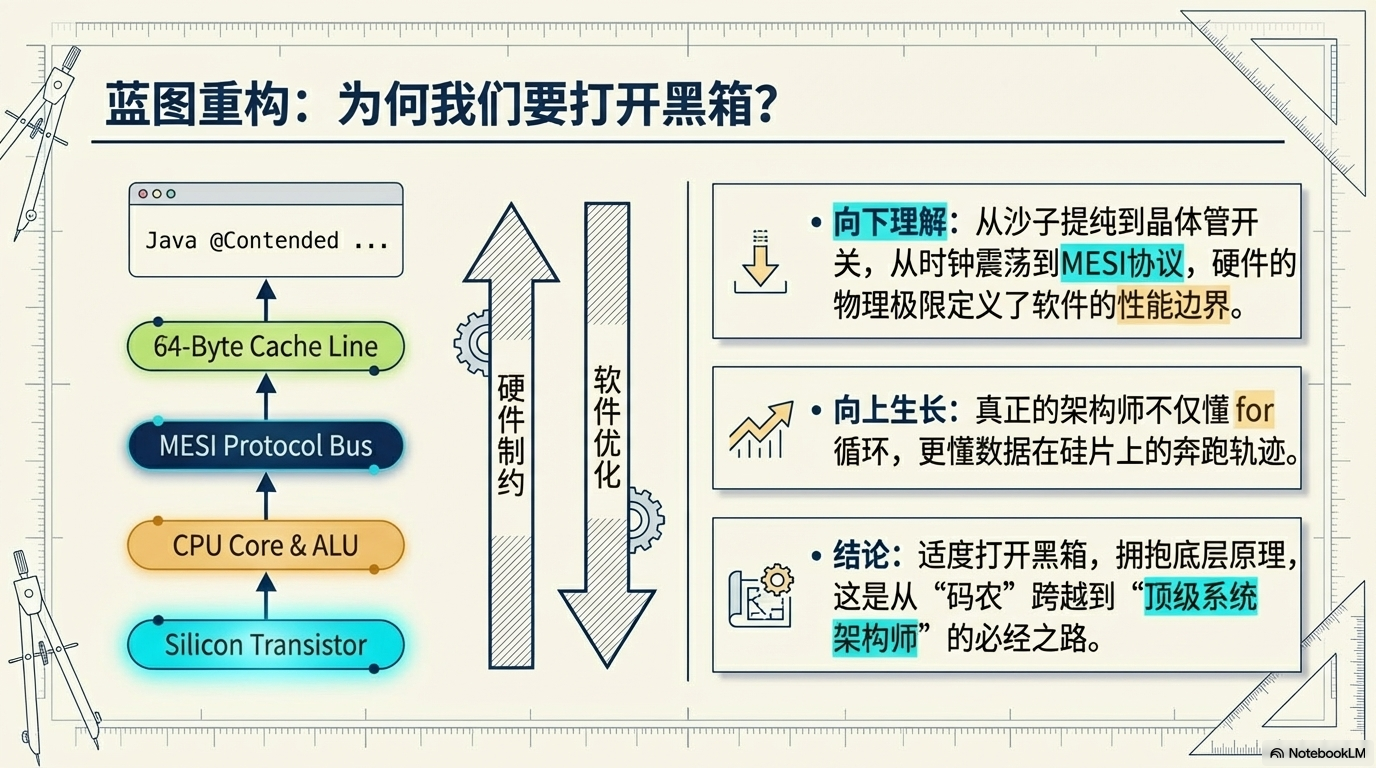

十三、蓝图重构:为什么要打开黑箱?

很多程序员只关注:

Java

Spring

MySQL

但忽略了底层。

真正的架构师会:

向下理解:

晶体管

CPU

缓存

一致性协议

向上构建:

高并发系统

分布式架构

性能优化

因为:

硬件的物理极限,决定了软件的性能边界。

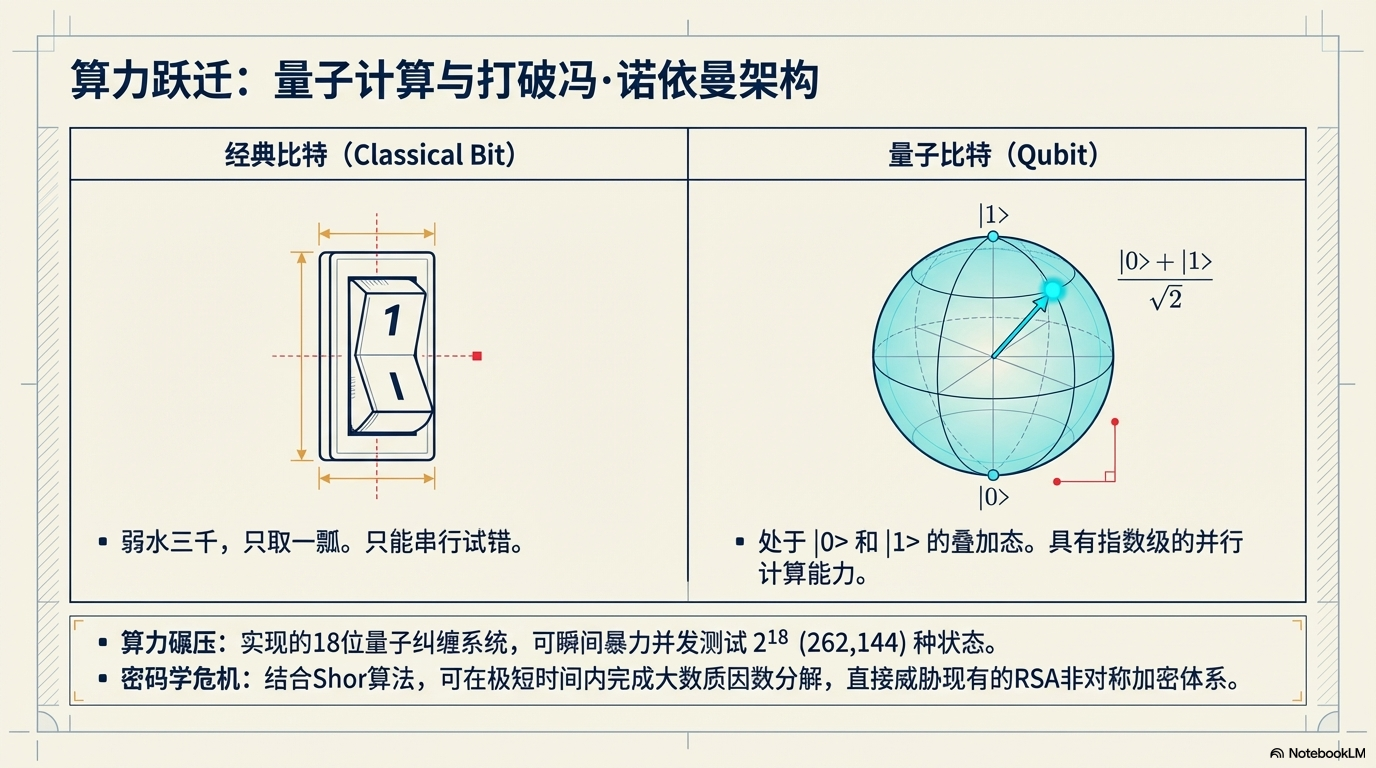

十四、算力跃迁:量子计算机

经典计算机使用:

bit

只能是:

0 或 1

而量子计算机使用:

Qubit

它可以处于:

0

1

或两者叠加

例如:

|0⟩ + |1⟩

量子计算的恐怖之处

经典计算:

一次只计算一种状态。

量子计算:

可以同时计算多个状态。

例如:

18个量子比特

可同时表示:

2^18 = 262144

种状态。

密码学危机

量子计算结合:

Shor算法

可以快速分解大整数。

意味着:

RSA

ECC

这些传统加密算法可能被破解。

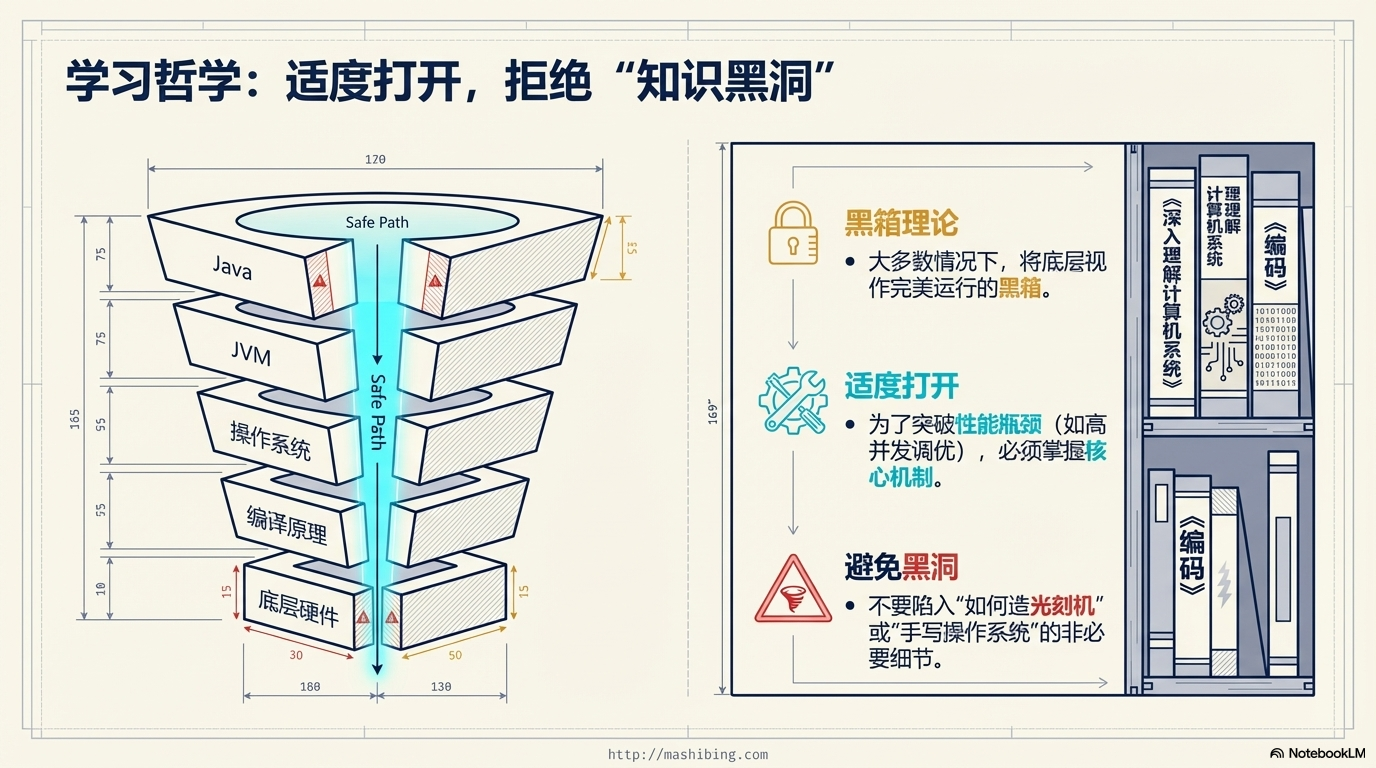

十五、学习的正确姿势

学习底层有三个原则。

1 黑箱理论

大多数情况下:

可以把系统当黑箱

2 适度打开

遇到性能瓶颈时:

必须理解:

- CPU

- Cache

- 内存模型

3 避免知识黑洞

不要陷入:

- 如何造光刻机

- 如何写操作系统

这些细节。

结语

从:

沙子 → 晶体管 → CPU → Cache → JVM → Java

这一整条链路,构成了现代软件世界。

理解这些底层原理,你会发现:

很多性能问题其实早已写在硬件里。

这就是:

从“码农”走向“系统架构师”的必经之路。

评论区